CMOS集成电路设计中逻辑门电路分析

在现代数字集成电路(IC)设计中,互补金属氧化物半导体(CMOS)技术因其低功耗、高噪声容限和优异的可扩展性而占据主导地位。逻辑门电路作为数字系统的基石,其性能、面积和功耗直接决定了整个芯片的效能。因此,对CMOS逻辑门电路进行深入分析是集成电路设计的核心环节。

一、CMOS逻辑门的基本结构与工作原理

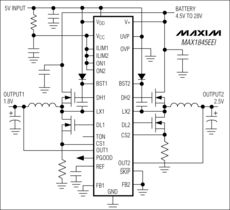

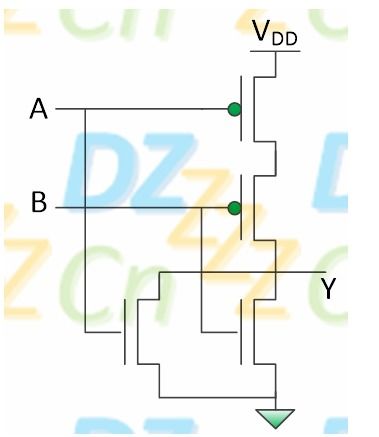

CMOS逻辑门的基本结构由一对互补的MOSFET(金属氧化物半导体场效应晶体管)构成:P型MOSFET(PMOS)和N型MOSFET(NMOS)。PMOS管作为上拉网络(PUN),负责在输出逻辑“1”时连接电源(VDD);NMOS管作为下拉网络(PDN),负责在输出逻辑“0”时连接地(GND)。这种互补结构确保了在稳态下,从电源到地的直接通路被阻断,从而实现了极低的静态功耗。

以最基本的CMOS反相器(非门)为例:一个PMOS管和一个NMOS管串联,栅极相连作为输入端,漏极相连作为输出端。当输入为低电平时,PMOS导通,NMOS截止,输出被上拉至高电平;当输入为高电平时,PMOS截止,NMOS导通,输出被下拉至低电平。其他复杂逻辑门(如与非门、或非门)则是通过将多个PMOS和NMOS管以特定方式组合,分别构成上拉和下拉网络来实现的。

二、关键性能参数分析

在集成电路设计中,对逻辑门电路的性能分析主要围绕以下几个关键参数展开:

- 延迟时间:信号从输入变化到输出稳定所需的时间,主要包括上升时间(Tr)和下降时间(Tf)。延迟受晶体管的尺寸(宽长比)、负载电容、互连线电容以及输入信号边沿速率的影响。通过优化晶体管尺寸和布局,可以平衡速度与功耗。

- 功耗:

- 静态功耗:在稳定状态下,CMOS逻辑门由于没有直流通路,理论上静态功耗近乎为零,但实际上存在亚阈值漏电流和栅极漏电流。

- 动态功耗:主要由电路开关过程中的电容充放电(P = α C VDD² * f)和短路电流(在输入信号跳变期间,PMOS和NMOS短暂同时导通)产生。降低电源电压(VDD)是减少动态功耗最有效的方法之一。

- 噪声容限:指电路在存在噪声干扰时仍能正确识别逻辑电平的能力。它由电压传输特性(VTC)曲线决定,通常用高电平噪声容限(NMH)和低电平噪声容限(NML)来量化。稳健的设计需要足够的噪声容限以应对工艺偏差和环境变化。

- 扇入与扇出:扇入指一个逻辑门的输入端口数量;扇出指一个逻辑门能够驱动的同类门数量。扇出过大(重负载)会显著增加延迟,设计中需要进行缓冲或调整驱动能力。

三、设计考量与优化技术

- 晶体管尺寸缩放:根据逻辑功能,合理设置PMOS与NMOS的宽长比。通常,为了获得对称的上升/下降时间,PMOS管的宽度需要设计为NMOS管的2到3倍(因为空穴迁移率低于电子迁移率)。

- 逻辑努力理论:一种系统化的延迟建模与优化方法,通过将路径延迟分解为逻辑努力、电气努力和分支努力,帮助设计者快速估算和优化多级逻辑链的性能,找到最佳的级数和晶体管尺寸。

- 功耗-性能-面积(PPA)权衡:这是集成电路设计的永恒主题。提高速度往往需要更大的晶体管(增加面积和功耗),而降低功耗又可能牺牲性能。设计者需根据应用场景(如高性能计算、移动设备)确定优化优先级。

- 工艺角与变异分析:在实际制造中,工艺参数(如晶体管阈值电压、沟道长度)会在一定范围内波动。设计必须通过仿真覆盖典型(TT)、快(FF)、慢(SS)等多个工艺角,以及考虑电压、温度(PVT)变化,确保电路在所有条件下都能可靠工作。

四、先进CMOS逻辑结构

随着工艺节点不断微缩,传统CMOS结构面临挑战,衍生出一些变体:

- 传输门逻辑:利用PMOS和NMOS并联构成近乎理想的开关,用于构建多路选择器、锁存器等。

- 动态逻辑:通过预充电和求值两个阶段工作,减少了实现复杂逻辑所需的晶体管数量,速度更快,但存在电荷泄漏和噪声敏感等问题。

- 多米诺逻辑:动态逻辑与静态反相器的结合,兼具高速和驱动能力强的优点,广泛用于高性能数据路径中。

###

对CMOS逻辑门电路的深入分析是成功进行集成电路设计的基础。从基本原理出发,精确建模其延迟、功耗和噪声特性,并运用逻辑努力等优化方法,设计者能够在功耗、性能和面积之间取得最佳平衡。随着技术发展,新的器件结构和设计方法论不断涌现,但掌握这些核心分析技能,依然是应对未来更复杂、更先进芯片设计挑战的关键。

如若转载,请注明出处:http://www.yunkudou.com/product/44.html

更新时间:2026-04-16 11:08:10