CMOS集成电路设计(二) 接口电路详解

在CMOS集成电路设计中,接口电路是连接芯片内部核心逻辑与外部世界的关键桥梁。它的性能直接影响着整个系统的可靠性、速度、功耗以及抗干扰能力。本文作为CMOS集成电路设计系列的第二部分,将深入解析几种核心的接口电路。

一、输入接口电路

输入接口电路的主要任务是将来自外部(如其他芯片、传感器或开关)的信号,转换成芯片内部CMOS逻辑能够安全、可靠识别的电压电平。

- 施密特触发器输入缓冲器:这是最常用的输入接口之一。其核心特点是具有滞回特性,即高、低电平的翻转阈值不同。这能有效抑制输入信号上的噪声和振铃现象,提供干净的信号给内部电路,特别适用于处理缓慢变化或噪声较大的信号,如按键输入。

- 电平转换输入缓冲器:当芯片需要与不同供电电压的器件通信时(例如,内核1.2V供电,但需要接收3.3V的输入信号),就需要电平转换电路。它通常采用特殊的晶体管结构或级联方式,确保高电压信号能被安全地转换为内部低电压电平,同时避免栅氧过压损坏。

二、输出接口电路

输出接口电路负责将芯片内部微弱的逻辑信号,驱动到能够满足外部负载(如PCB走线、其他芯片的输入电容)要求的电流和电压水平。

- 推挽输出驱动器:这是最标准的CMOS输出级,由一个PMOS上拉管和一个NMOS下拉管串联构成。它能够提供完整的轨到轨(从VDD到GND)电压摆幅,并且通过调整晶体管的宽长比(W/L),可以设计出从轻负载到重负载(如驱动LED、继电器)的各种驱动能力。设计时需要仔细权衡驱动能力、开关速度、功耗和面积。

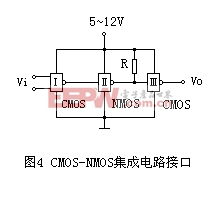

- 开漏输出:这种输出结构只有NMOS下拉管,没有内部上拉。输出端需要通过外部上拉电阻连接到电源。其最大优势是可以实现“线与”功能,即多个开漏输出可以直接连接在一起,只要有一个输出为低,总线即为低。这在I2C等总线协议中被广泛使用。它也便于实现不同电压域之间的电平转换。

三、双向接口(I/O)电路

在现代芯片中,许多引脚被设计为既可以作为输入也可以作为输出,即双向I/O端口。其核心是一个三态控制逻辑。

- 当设置为输出模式时,使能输出驱动器,内部逻辑信号被推送到引脚。

- 当设置为输入模式时,输出驱动器被置于高阻态(关闭),引脚上的信号通过输入缓冲器传入内部。

设计双向I/O时,必须避免输出使能和输入信号冲突导致的“总线竞争”和过大短路电流,同时需要处理好信号方向切换时的时序问题。

四、特殊接口电路

- 静电放电保护电路:所有与外部连接的引脚都必须集成ESD保护结构,通常采用二极管、栅接地NMOS或硅控整流器等方式,将人体模型或机器模型放电产生的高压大电流泄放到电源或地,保护内部脆弱的栅氧。

- 差分信号接口:对于高速或高抗噪声要求的传输(如LVDS、USB),常采用差分对作为接口。它使用两根线传输相位相反的信号,接收端检测两者的电压差。这种结构对共模噪声有极强的抑制能力,并能以更低的电压摆幅实现高速数据传输,从而降低功耗和EMI。

接口电路设计是CMOS集成电路设计中工程性与艺术性并重的环节。设计师需要在速度、功耗、面积、鲁棒性和兼容性之间取得最佳平衡。理解并熟练掌握各种接口电路的工作原理与设计要点,是确保芯片在复杂系统中稳定工作的基石。随着工艺演进和系统需求的变化,新型的接口电路技术(如基于SerDes的高速串行接口)也在不断发展,持续学习是设计者的必备素养。

如若转载,请注明出处:http://www.yunkudou.com/product/16.html

更新时间:2026-04-16 15:08:50